Proposal for a joint "équipe projet commune" (joint project team).

Lyon 1

# CASH: Compilation and Analysis, Software and Hardware

# December 10, 2018

Name: CASH: Compilation and Analysis, Software and Hardware

Laboratory: Laboratoire d'Informatique du Parallélisme, Lyon, France

Research Institutes (tutelles): CNRS, ENS-Lyon, Inria, UCBL

Inria research field: Algorithmics, Programming, Software and Architecture / Architecture, Languages and Compilation

Scientific leader: Matthieu Moy

Members:

Christophe Alias (Researcher, Inria)

Julien Braine (Ph.D student)

Laure Gonnord (Associate Professor, Univ. Lyon1)

Ludovic Henrio (Researcher, CNRS)

Paul Iannetta (Ph.D student)

Laetitia Lecot (Inria assistant)

Matthieu Moy (Team Leader, Associate Professor, Univ. Lyon1)

# Contents

| 1 | Introduction                                                    | 2      |

|---|-----------------------------------------------------------------|--------|

|   | 1.1 Scientific Context                                          | <br>2  |

|   | 1.2 Scientific Foundations and Transversal Topics               | <br>3  |

|   | 1.3 Research Objectives                                         | <br>4  |

|   | 1.4 Overall Approach                                            | <br>5  |

|   | 1.5 Application Domains                                         | <br>5  |

| 2 | Research Directions                                             | 6      |

|   | 2.1 Definition of dataflow representations of parallel programs | <br>6  |

|   | 2.2 Expressivity and Scalability of Static Analyses             | <br>9  |

|   | 2.3 Compiling and Scheduling Dataflow Programs                  | <br>11 |

|   | 2.4 HLS-specific Dataflow Optimizations                         | <br>14 |

|   | 2.5 Simulation of Hardware                                      | 16     |

| 3 | Research group                                                  | 18     |

| 4 | Positioning with Respect to Other Research Teams                | 19     |

|   | 4.1 Research themes and related teams within Inria              | <br>20 |

|   | 4.2 Large-scale Computing                                       | <br>20 |

|   | 4.3 High Level Synthesis                                        | <br>20 |

|   | 4.4 Code Optimization and Execution                             | <br>21 |

|   | 4.5 Abstract Interpretation and Formal Methods                  | <br>21 |

LIP – UMR CNRS / ENS Lyon / UCB Lyon 1 / Inria – 69007 Lyon

|   | <ul><li>4.6 Dataflow</li></ul>                                              |      |

|---|-----------------------------------------------------------------------------|------|

| 5 | Industrial collaborations                                                   | 22   |

|   | 5.1 XtremLogic                                                              | . 22 |

|   | 5.2 STMicroelectronics                                                      | . 22 |

|   | 5.3 Kalray                                                                  | . 23 |

| 6 | Relevant publications of the team members                                   | 23   |

| A | Appendix: Details on Positioning and Added Value                            | 29   |

|   | A.1 Other teams inside LIP                                                  | . 29 |

|   | A.2 CORSE                                                                   | . 30 |

|   | A.3 SOCRATE                                                                 | . 31 |

|   | A.4 Synchrone (Verimag)                                                     | . 33 |

|   | A.5 SPADES                                                                  | . 34 |

|   | A.6 TEA                                                                     | . 34 |

|   | A.7 PARKAS                                                                  | . 35 |

|   | A.8 Scale                                                                   | . 35 |

|   | A.9 Kairos                                                                  |      |

|   | A.10 PACSS (Verimag), ANTIQUE (Paris), CELTIQUE (Rennes)                    | . 36 |

|   | A.11 CAIRN                                                                  | . 38 |

|   | A.12 MOCS                                                                   | . 39 |

|   | A.13 DATAMOVE                                                               |      |

|   | A.14 Other Inria teams of the theme "Architecture, languages, compilation"  | . 39 |

|   | A.15 System-Level Synthesis (TIMA)                                          |      |

|   | A.16 Département Architectures Conception et Logiciels Embarqués (CEA LIST) |      |

|   | A.17 CIAN - Analog and Digital Integrated Circuit (LIP6)                    |      |

|   | A.18 International projects and teams                                       | . 40 |

# 1 Introduction

### 1.1 Scientific Context

The advent of parallelism in supercomputers and in more classical end-user computers increases the need for high-level code optimization and improved compilers.

Until 2006, the typical power-consumption of a chip remained constant for a given silicon area as the transistor size decreased (this evolution is referred to as Dennard scaling). In other words, energy efficiency was following an exponential law similar to Moore's law. This is no longer true, hence radical changes are needed to further improve power efficiency, which is the limiting factor for large-scale computing. Improving the performance under a limited energy budget must be done by rethinking computing systems at all levels: hardware, software, compilers, and runtimes.

On the hardware side, new architectures such as multi-core processors, Graphics Processing Units (GPUs), many-core and FPGA accelerators are introduced, resulting into complex heterogeneous platforms. In particular, FPGAs are now a credible solution for energy-efficient HPC. An FPGA chip can deliver the same computing power as a GPU for an energy budget 10 times smaller. A consequence of this diversity and heterogeneity is that a given computation can be implemented in many different ways, with different performance characteristics. An obvious example is changing the degree of parallelism: this allows trading execution time for number of cores used. However, many choices are less obvious: for example, augmenting the degree of parallelism of a memory-bounded application will not improve performance. Most architectures involve a complex memory hierarchy, hence memory access patterns have a considerable impact on performance too. The design-space to be explored to find the best performance is much wider than it used to be with older architectures, and new tools are needed to help the programmer explore it. The problem is even stronger for FPGA accelerators, where programmers are expected to design a circuit for their application! Traditional synthesis tools take as input low-level languages like VHDL and Verilog. As opposed to this, high-level languages and hardware compilers (HLS, High-Level Synthesis, that takes as input a C or C-like language and produces a circuit description) are required.

One of the bottlenecks of performance and energy efficiency is data movement. The operational intensity (ratio computation/communication) must be optimized to avoid memory-bounded performance. Compiler analyses are strongly required to explore the trade-offs (operational intensity vs. local memory size, operational intensity vs. peak performance for reconfigurable circuits).

These issues are considered as one of the main challenges in the Hipeac roadmap [21] which, among others, cites the two major issues:

- Applications are moving towards global-scale services, accessible across the world and on all devices. Low power processors, systems, and communications are key to computing at this scale. (*Strategic Area 2, Data Center Computing*).

- Today data movement uses more power than computation. [...] To adapt to this change, we need to expose data movement in applications and optimize them at runtime and compile time and to investigate communication-optimized algorithms (*cross-cutting challenge 1, energy efficiency*).

#### 1.2 Scientific Foundations and Transversal Topics

#### 1.2.1 Parallelism and Dataflow

Parallelism based on dataflow is one way to tackle energy-efficiency and get control on data movement. The dataflow formalism expresses a computation on an infinite number of values, that can be viewed as successive values of a variable during time. A dataflow program is structured as a set of *processes* that communicate values through *buffers*.

Examples of dataflow languages include the synchronous languages Lustre [31] and Signal [35]. SigmaC [9] is a dataflow oriented programming language dedicated to HPC. The DPN representation [4] (data-aware process network) is an example of a dataflow intermediate representation for a parallelizing compiler.

A dataflow program or representation can be implemented in several ways: as software running either on a parallel general-purpose architecture or on accelerators like GPUs or many-cores, or as hardware implementation, possibly running on reconfigurable chips (FPGAs).

Dataflow formalisms are a transverse topic of this proposal. We plan to use them both as programming languages and as intermediate representations within compilers. However, we will not a priori restrict ourselves to dataflow applications (we also consider approaches to optimize languages dedicated to GPU like CUDA and OpenCL code for example). We believe that the dataflow formalism is a good starting point and a convergence point for all the members of the team.

#### 1.2.2 Automatic Parallelization and Polyhedral Model

The main challenge of automatic parallelization is to reason about the computation. With the polyhedral model, the iterations of compute-intensive loop kernels are abstracted away as integral points satisfying affine constraints (i.e., set of points in a polyhedron). This way, precise, *iteration-level*, compiler analyses and optimizations can be performed thanks to geometric operations and linear optimization (to quote a few: dataflow analysis [22], scheduling [14], memory allocation [1]).

Historically, the polyhedral model focused on loop kernels with *Affine Control Loops* (ACL). An ACL program satisfies the following properties: (i) only for loops and if conditions operating on arrays (ii) the loop bounds, conditions and array accesses are affine functions of surrounding loop counters and structure parameters (typically the array size). This should *not* be viewed as a limitation, but only as one possible use case. Actually, the polyhedral model could apply to *any* program providing the right *abstraction* of iterations as polyhedra. How to find the right level of abstraction and granularity is a transverse issue addressed in Sections 2.1 and 2.3.

In particular, we plan to explore the extensions of polyhedral techniques to handle irregular programs with while loops and complex data structures (such as trees and lists). This raises many issues. We cannot represent finitely all the possible executions traces. Which approximation/representation to choose? Then, how to adapt existing techniques on approximated traces while preserving correctness?

#### 1.3 Research Objectives

The overall objective of the CASH team is to take advantage of the characteristics of the specific hardware (generic hardware, hardware accelerators, or reconfigurable chips) to *compile energy efficient software and hardware*. More precisely, we plan to work on:

- 1. Definition of dataflow representations of parallel programs that can capture the parallelism at all levels: fine-grain vs. coarse-grain, data & task parallelism, programming language, and intermediate representation (Section 2.1).

- 2. Scalable and expressive static program analyses. CASH will work on improving the scalability of analyses to allow a global analysis of large-scale programs, and on the expressiveness of analysis to find better program invariants. Analysis will be performed both on the representation defined above and on general programs (Section 2.2).

- 3. Transformations from and to the dataflow representation, combining traditional tools dedicated to dataflow and specific methods like the polyhedral model (Section 2.3).

- 4. A high-level synthesis (HLS) tool, built on the above item (instantiated with the particularities of FPGAs) and a code generation tool (Section 2.4). This HLS tool will focus on early stages of compilation and rely on an external tool for the back-end.

- 5. A parallel and scalable simulation of hardware systems, which, combined with the preceding activity, will result in an end-to-end workflow for circuit design (Section 2.5).

To ensure the coherency and the correctness of our approach these different tasks will rely on a *precise definition of the manipulated languages and their semantics*. The formalization of the different representations of the programs and of the analyses will allow us to show that these different tasks will be performed with the same understanding of the program semantics.

Note that these directions are strongly tied together. We use 5 research axis for the sake of the presentation, but their complementarity enables each member of the team to share common research goals while having their own research directions. Most of our results will contribute to several directions.

#### 1.4 Overall Approach

- · Cross-fertilization with several scientific communities.

- Case-study driven approach and transfer.

The CASH team targets applied research, in the sense that most research topics are driven by actual needs, discussed either through industrial partnership (see Section 5) or extracted from available benchmarks (e.g. Polybench [45]). We target a balance between theory and practice: problems extracted from industrial requirements often yield theoretical problems.

Our approach is to cross-fertilize between several communities. For example, the abstract interpretation community provide a sound theoretical framework and very powerful analysis, but these are rarely applied in the context of optimizing compilation. Similarly, the hardware simulation community usually considers compilers as black-boxes and do not interact with researchers in compilation.

Our contributions are therefore expected in several domains. While a global approach links CASH activities and members (see Section 2), we do not plan to have a single unified toolchain where all contributions will be implemented. For example, contributions in the domain of static analysis of sequential programs may be implemented in the LLVM tool, results on dataflow models are applied both in the SigmaC compiler and in the DCC HLS tool, ... This also implies that different activities of CASH target different application domains and potential end-users.

#### **1.5 Application Domains**

- Objective: analyze, compile, generate code, simulate HPC programs for various platforms.

- Unified approach but various application domains.

- Hard lock: **parallelism everywhere**  $\rightsquigarrow$  study various applications from different domains to validate our models and tools.

- Typical applications: HPC kernels, streaming and dataflow applications.

The CASH team targets HPC programs, at different levels. Small computation kernels (tens of lines of code) that can be analyzed and optimized aggressively, medium-size kernels (hundreds of lines of code) that require modular analysis, and assembly of compute kernels (either as classical imperative programs or written directly in a dataflow language).

The work on various application domains and categories of programs is driven by the same idea: exploring various topics is a way to converge on unifying representations and algorithms even for specific applications. All these applications share the same research challenge: find a way to integrate computations, data, mapping, and scheduling in a common analysis and compilation framework.

Typical HPC kernels include linear solvers, stencils, matrix factorizations, BLAS kernels, etc. Many kernels can be found in the Polybench/C benchmark suite [45]. The irregular versions can be found in [46]. Numerical kernels used in quantitative finance [58] are also good candidates, e.g., finite difference and Monte-Carlo simulation.

The medium-size applications we target are streaming algorithms [6], scientific workflows [53], and also the now very rich domain of deep learning applications [34]. We explore the possibilities of writing (see Section 2.1) and compiling (see Section 2.3) applications using a dataflow language. As a first step,

CASH: CNRS/ENSL/UCBL/Inria joint team proposal, 2018

we will target dataflow programs written in SigmaC [9] for which the fine grain parallelism is not taken into account. In parallel, we will also study the problem of deriving relevant (with respect to safety or optimization) properties on dataflow programs with array iterators.

The scientific focus of CASH is on compute kernels and assembly of kernels, and the first goal is to improve their efficient compilation. However the team will also work in collaboration with application developers, to understand better the overall need in HPC and design optimizations that are effective in the context of the targeted applications. In particular, we plan to collaborate with the Avalon team (LIP/Inria) that is expert in HPC applications and their design.

The approach of CASH is based on compilation, and our objective is to allow developers to design their own kernels, and benefit from good performance in terms of speed and energy efficiency without having to deal with fine-grained optimizations by hand. Consequently, our objective is first to improve the performance and energy consumption for HPC applications, while providing programming tools that can be used by developers and are at a convenient level of abstraction.

Obviously, large applications are not limited to assembly of compute kernels. Our languages and formalism definitions (2.1) and analyses (2.2) must also be able to deal with general programs. Our targets also include generalist programs with complex behaviors such as recursive programs operating on arrays, lists and trees; worklist algorithms (lists are not handled within the polyhedral domain). Analysis on these programs should be able to detect non licit memory accesses, memory consumption, hotspots, ..., and to prove functional properties.

The simulation activities (2.5) are both applied internally in CASH, to simulate intermediate representations, and for embedded systems. We are interested in Transaction-Level Models (TLM) of Systems-ona-Chip (SoCs) including processors and hardware accelerators. TLM provides an abstract but executable model of the chip, with enough details to run the embedded software. We are particularly interested in models written in a loosely timed coding style. We plan to extend these to heterogeneous simulations including a SystemC/TLM part to model the numerical part of the chip, and other simulators to model physical parts of the system.

## 2 Research Directions

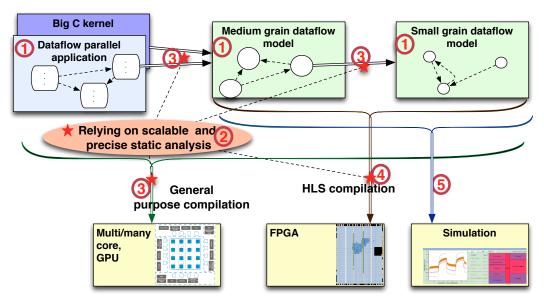

Figure 1 illustrates the organization of the research directions of our proposal (corresponding to the 5 research objectives stated in Section 1.3); the illustration relies on the flow of transformation steps performed to compile and simulate a source program. Each red rounded number represents one of the research directions presented below (e.g., static analysis -2 – is detailed in Section 2.2 below). We see at the same time that static analysis plays a central role to improve and contribute to many transformations, but also that our intermediate dataflow model (defined in Section 2.1) and the transformations from and to this model (described in Section 2.3) play a crucial role in the CASH proposal. We also see that we aim at taking as input both C programs, consisting of big kernels, typically a few hundred lines, but also bigger applications designed as a dataflow parallel program. Finally, the figure illustrates the three execution platforms we target, represented by the three last research directions below: general purpose compilation, HLS specific aspects (HLS compilation also relies on some results of general purpose compilation), and simulation.

### 2.1 Definition of dataflow representations of parallel programs

Figure 1: Organisation of research directions

- Objective: provide a unified intermediate representation for dataflow programs.

- Hard lock: **diversity of purpose**  $\rightsquigarrow$  design formal representation for proving correctness of optimization, and practical model on which efficient optimizations can be implemented.

In the last decades, several frameworks have emerged to design efficient compiler algorithms. The efficiency of all the optimizations performed in compilers strongly relies on effective *static analyses* and *intermediate representations*. Dataflow models are a natural intermediate representation for hardware compilers (HLS) and more generally for parallelizing compilers. Indeed, dataflow models capture task-level parallelism and can be mapped naturally to parallel architectures. In a way, a dataflow model is a partition of the computation into processes and a partition of the flow dependences into channels. This partitioning prepares resource allocation (which processor/hardware to use) and medium-grain communications.

The main goal of the CASH team is to provide efficient analyses and the optimizing compilation frameworks for dataflow programming models. The results of the team will rely on programming languages and representation of programs in which parallelism and dataflow play a crucial role. This first research direction aims at defining these dataflow languages and intermediate representations, both from a practical perspective (syntax or structure), and from a theoretical point of view (semantics). This first research direction thus defines the models on which the other directions will rely. It is important to note that we do not restrict ourself to a strict definition of dataflow languages and, more generally, we are interested in the parallel languages in which dataflow synchronization plays a significant role.

*Intermediate dataflow model.* The intermediate dataflow model is a representation of the program that is adapted for optimization and scheduling. It will be obtained from the analysis of a (parallel or sequential) program and should at some point be used for compilation. The dataflow model must specify precisely its semantics and parallelism granularity. It must also be analyzable with polyhedral techniques, where powerful concepts exist to design compiler analysis, e.g., scheduling or resource allocation. Polyhedral

Process Networks [56] extended with a module system could be a good starting point. But then, how to fit non-polyhedral parts of the program? A solution is to hide non-polyhedral parts into processes with a proper polyhedral abstraction. This organization between polyhedral and non-polyhedral processes will be a key aspect of our medium-grain dataflow model. The design of our intermediate dataflow model and the precise definition of its semantics will constitute a reliable basis to formally define and ensure the correctness of algorithms proposed by CASH: compilation, optimizations and analyses.

Dataflow programming languages. Dataflow paradigm has also been explored quite intensively in programming languages. Indeed, there exists a large panel of dataflow languages, whose characteristics differ notably, the major point of variability being the scheduling of agents and their communications. There is indeed a continuum from the synchronous dataflow languages like Lustre [31] or Streamit [52], where the scheduling is fully static, and general communicating networks like KPNs [33] or RVC-Cal [6] where a dedicated runtime is responsible for scheduling tasks dynamically, when they *can* be executed. These languages share some similarities with actor languages that go even further in the decoupling of processes by considering them as independent reactive entities. Another objective of the CASH team is to study dataflow programming *languages*, their semantics, their expressiveness, and their compilation. The specificity of the CASH team will be that these languages will be designed taking into consideration the compilation using polyhedral techniques. In particular, we will explore which dataflow constructs are better adapted for our static analysis, compilation, and scheduling techniques. In practice we want to propose high-level primitives to express data dependency, this way the programmer will express parallelism in a dataflow way instead of the classical communication-oriented dependencies. The higher-level more declarative point of view will make programming easier but also give more optimization opportunities. These primitives will be inspired by the existing works in the polyhedral model framework, as well as dataflow languages, but also in the actors and active object languages [13] that nowadays introduce more and more dataflow primitives to enable data-driven interactions between agents, particularly with futures [16, 25].

#### 2.1.1 Expected Impact

Consequently, the impact of this research direction is both the usability of our representation for static analyses and optimizations performed in Sections 2.2 and 2.3, and the usability of its semantics to prove the correctness of these analyses.

#### 2.1.2 Scientific Program

**Short-term and ongoing activities.** We obtained preliminary experimental [3, 4, 26] and theoretical [32] results, exploring several aspects of dataflow models. The next step is to define accurately the intermediate dataflow model and to study existing programming and execution models:

- Define our medium-grain dataflow model. So far, a modular Polyhedral Process Networks appears as a natural candidate but it may need to be extended to be adapted to a wider range of applications. Precise semantics will have to be defined for this model to ensure the articulation with the activities discussed in Section 2.3.

- Study precisely existing dataflow languages, their semantics, their programmability, and their limitations.

**Medium-term activities.** In a second step, we will extend the existing results to widen the expressiveness of our intermediate representation and design new parallelism constructs. We will also work on the semantics of dataflow languages:

- Propose new stream programming models and a clean semantics where all kinds of parallelisms are expressed explicitly, and where all activities from code design to compilation and scheduling can be clearly expressed.

- Identify a core language that is rich enough to be representative of the dataflow languages we are interested in, but abstract and small enough to enable formal reasoning and proofs of correctness for our analyses and optimizations.

**Long-term activities.** In a longer-term vision, the work on semantics, while remaining driven by the applications, would lead to to more mature results, for instance:

- Design more expressive dataflow languages and intermediate representations which would at the same time be expressive enough to capture all the features we want for aggressive HPC optimizations, and sufficiently restrictive to be (at least partially) statically analyzable at a reasonable cost.

- Define a module system for our medium-grain dataflow language. A program will then be divided into modules that can follow different compilation schemes and execution models but still communicate together. This will allow us to encapsulate a program that does not fit the polyhedral model into a polyhedral one and vice versa. Also, this will allow a compositional analysis and compilation, as opposed to global analysis which is limited in scalability.

### 2.2 Expressivity and Scalability of Static Analyses

- Objective: design safe and efficient compilers for general programs.

- Hard lock: scalability ~> design lowcost analyses tailored to state-of-the-art optimizations.

The design and implementation of efficient compilers becomes more difficult each day, as they need to bridge the gap between *complex languages* and *complex architectures*. Application developers use languages that bring them close to the problem that they need to solve which explains the importance of high-level programming languages. However, high-level programming languages tend to become more distant from the hardware which they are meant to command.

In this research direction, we propose to design expressive and scalable static analyses for compilers. This topic is closely linked to Sections 2.1 and 2.3 since the design of an efficient intermediate representation is made while regarding the analyses it enables. The intermediate representation should be expressive enough to embed maximal information; however if the representation is too complex the design of scalable analyses will be harder.

The analyses we plan to design in this activity will of course be mainly driven by the HPC dataflow optimizations we mentioned in the preceding sections; however we will also target other kinds of analyses applicable to more general purpose programs. We will thus consider two main directions:

• Extend the applicability of the polyhedral model, in order to deal with HPC applications that do not fit totally in this category. More specifically, we plan to work on more complex control and also on complex data structures, like sparse matrices, which are heavily used in HPC.

• Design of specialized static analyses for memory diagnostic and optimization inside general purpose compilers.

For both activities, we plan to cross fertilize ideas coming from the abstract interpretation community as well as language design, dataflow semantics, and WCET estimation techniques.

*Correct by construction analyses.* The design of well-defined semantics for the chosen programming language and intermediate representation will allow us to show the correctness of our analyses. The precise study of the semantics of Section 2.1 will allow us to adapt the analysis to the characteristics of the language, and prove that such an adaptation is well founded. This approach will be applicable both on the source language and on the intermediate representation.

Such wellfoundedness criteria relatively to the language semantics will first be used to design our analyses, and then to study which extensions of the languages can be envisioned and analyzed safely, and which extensions (if any) are difficult to analyze and should be avoided. Here the correct identification of a core language for our formal studies (see Section 2.1) will play a crucial role as the core language should feature all the characteristics that might make the analysis difficult or incorrect.

*Scalable abstract domains.* We already have experience in designing low-cost semi relational abstract domains for pointers [43, 36], as well as tailoring static analyses for specialized applications in compilation [24, 50], Synchronous Dataflow scheduling [49], and extending the polyhedral model to irregular applications [2]. We also have experience in the design of various static verification techniques adapted to different programming paradigms.

#### 2.2.1 Expected impact

The long-term expected impact of this work is the significantly widened applicability of various tools or compilers related to parallelization. We consider two main goals: extend the applicability of heavyweight analysis and parallelization techniques to a wider class of programs, and leverage the applicability of *abstract domains* so that they could be used as analysis passes for client analyses/optimizations in state-of-the-art compiler infrastructures such as LLVM.

We target both analysis for optimization and analysis to detect bugs, or prove their absence (numerical overflows in sequential code, parallel bugs, proving program termination, detecting transient errors, ...). We rely on the polyhedral model and on abstract interpretation, both of which are already used for this purpose.

In a longer term, we expect to be able to design abstract domains tailored for application and platform, and apply them to domain specific languages compiled and run on multicore systems as well as specific machines, without reinventing complete toolchains.

#### 2.2.2 Scientific Program

**Short-term and ongoing activities.** Together with Paul Iannetta and Lionel Morel (INSA/CEA LETI), we are currently working on the *semantic rephrasing* of the polyhedral model [28]. The objective is to clearly redefine the key notions of the polyhedral model on general flowchart programs operating on arrays, lists and trees. We reformulate the algorithms that are performed to compute dependencies in a more semantic fashion, i.e. considering the program semantics instead of syntactical criteria. The next step is to express classical scheduling and code generation activities in this framework, in order to overcome the classical syntactic restrictions of the polyhedral model.

**Medium-term activities.** In medium term, we want to extend the polyhedral model for more general data-structures like lists and sparse matrices. For that purpose, we need to find polyhedral (or other shapes) abstractions for non-array data-structures; the main difficulty is to deal with non-linearity and/or partial information (namely, over-approximations of the data layout, or over-approximation of the program behavior). This activity will rely on a formalization of the optimization activities (dependency computation, scheduling, compilation) in a more general Abstract-Interpretation based framework in order to make the approximations explicit.

At the same time, we plan to continue to work on scaling static analyses for general purpose programs, in the spirit of Maroua Maalej's PhD [37], whose contribution is a sequence of memory analyses inside production compilers. We already began a collaboration with Sylvain Collange (PACAP team of IRISA Laboratory) on the design of static analyses to optimize copies from the global memory of a GPU to the block kernels (to increase locality). In particular, we have the objective to design specialized analyses but with an explicit notion of cost/precision compromise, in the spirit of the paper [30] that tries to formalize the cost/precision compromise of interprocedural analyses with respect to a "context sensitivity parameter".

**Long-term activities.** In a longer-term vision, the work on scalable static analyses, whether or not directed from the dataflow activities, will be pursued in the direction of large general-purpose programs.

An ambitious challenge is to find a generic way of adapting existing (relational) abstract domains within the Single Static Information [7] framework so as to improve their scalability. With this framework, we would be able to design static analyses, in the spirit of the seminal paper [18] which gave a theoretical scheme for classical abstract interpretation analyses.

We also plan to work on the interface between the analyses and their optimization clients inside production compilers.

#### 2.3 Compiling and Scheduling Dataflow Programs

- Objective: design an end-to-end compiler/scheduler for middle-sized dataflow intensive applications.

- Hard locks: **granularity** ~>> combining tools from the polyhedral model and dataflow paradigms.

In this part, we propose to design the compiler analyses and optimizations for the *medium-grain* dataflow model defined in section 2.1. We also propose to exploit these techniques to improve the compilation of dataflow languages based on actors. Hence our activity is split into the following parts:

- Translating a sequential program into a medium-grain dataflow model. The programmer cannot be expected to rewrite the legacy HPC code, which is usually relatively large. Hence, compiler techniques must be invented to do the translation.

- Transforming and scheduling our medium-grain dataflow model to meet some classic optimization criteria, such as throughput, local memory requirements, or I/O traffic.

- Combining agents and polyhedral kernels in dataflow languages. We propose to apply the techniques above to optimize the processes in actor-based dataflow languages and combine them with the parallelism existing in the languages.

We plan to rely extensively on the polyhedral model to define our compiler analysis. The polyhedral model was originally designed to analyze imperative programs. Analysis (such as scheduling or buffer allocation) must be redefined in light of dataflow semantics.

*Translating a sequential program into a medium-grain dataflow model.* The programs considered are compute-intensive parts from HPC applications, typically big HPC kernels of several hundreds of lines of C code. In particular, we expect to analyze the process code (actors) from the dataflow programs. On short ACL (Affine Control Loop) programs, direct solutions exist [54] and rely directly on array dataflow analysis [22]. On bigger ACL programs, this analysis no longer scales. We plan to address this issue by *modularizing* array dataflow analysis. Indeed, by splitting the program into processes, the complexity is mechanically reduced. This is a general observation, which was exploited in the past to compute schedules [23]. When the program is no longer ACL, a clear distinction must be made between polyhedral parts and non polyhedral parts. Hence, our medium-grain dataflow language must distinguish between polyhedral process networks, and non-polyhedral code fragments. This structure raises new challenges: How to abstract away non-polyhedral parts while keeping the polyhedrality of the dataflow program? Which trade-off(s) between precision and scalability are effective?

*Medium-grain data transfers minimization.* When the system consists of a single computing unit connected to a slow memory, the roofline model [57] defines the optimal ratio of computation per data transfer (*operational intensity*). The operational intensity is then translated to a partition of the computation (loop tiling) into *reuse units*: inside a reuse unit, data are transfered locally; between reuse units, data are transfered through the slow memory. On a *fine-grain* dataflow model, reuse units are exposed with loop tiling; this is the case for example in Data-aware Process Network (DPN) [4]. The following questions are however still open: How does that translate on *medium-grain* dataflow models? And fundamentally what does it mean to *tile* a dataflow model?

*Combining agents and polyhedral kernels in dataflow languages.* In addition to the approach developed above, we propose to explore the compilation of dataflow programming languages. In fact, among the applications targeted by the project, some of them are already thought or specified as dataflow actors (video compression, machine-learning algorithms,...).

So far, parallelization techniques for such applications have focused on taking advantage of the decomposition into agents, potentially duplicating some agents to have several instances that work on different data items in parallel [29]. In the presence of big agents, the programmer is left with the splitting (or merging) of these agents by-hand if she wants to further parallelize her program (or at least give this opportunity to the runtime, which in general only sees agents as non-malleable entities). In the presence of arrays and loop-nests, or, more generally, some kind of regularity in the agent's code, however, we believe that the programmer would benefit from automatic parallelization techniques such as those proposed in the previous paragraphs. To achieve the goal of a totally integrated approach where programmers write the applications they have in mind (application flow in agents where the agents' code express potential parallelism), and then it is up to the system (compiler, runtime) to propose adequate optimizations, we propose to build on solid formal definition of the language semantics (thus the formal specification of parallelism occurring at the agent level) to provide hierarchical solutions to the problem of compilation and scheduling of such applications.

#### 2.3.1 Expected impact

In general, splitting a program into simpler processes simplifies the problem. This observation leads to the following points:

- By abstracting away irregular parts in processes, we expect to structure the long-term problem of handling irregular applications in the polyhedral model. The long-term impact is to widen the applicability of the polyhedral model to irregular kernels.

- Splitting a program into processes reduces the problem size. Hence, it becomes possible to scale traditionally expensive polyhedral analysis such as scheduling or tiling to quote a few.

As for the third research direction, the short term impact is the possibility to combine efficiently classical dataflow programming with compiler polyhedral-based optimizations. We will first propose ad-hoc solutions coming from our HPC application expertise, but supported by strong theoretical results that prove their correctness and their applicability in practice. In the longer term, our work will allow specifying, designing, analyzing, and compiling HPC dataflow applications in a unified way. We target semi-automatic approaches where pertinent feedback is given to the developer during the development process.

### 2.3.2 Scientific Program

**Short-term and ongoing activities.** We are currently working on the RTM (Reverse-Time Migration) kernel for oil and gas applications ( $\approx$  500 lines of C code). This kernel is long enough to be a good starting point, and small enough to be handled by a polyhedral splitting algorithm. We figured out the possible splittings so the polyhedral analysis can scale and irregular parts can be hidden. In a first step, we plan to define splitting metrics and algorithms to optimize the usual criteria: communication volume, latency and throughput.

Together with Lionel Morel (INSA/CEA LETI), we currently work on the evaluation of the practical advantage of combining the dataflow paradigm with the polyhedral optimization framework. We empirically build a proof-of-concept tooling approach, using existing tools on existing languages [27]. We combine dataflow programming with polyhedral compilation in order to enhance program parallelization by leveraging both inter-agent parallelism and intra-agent parallelism (i.e., regarding loop nests inside agents). We evaluate the approach practically, on benchmarks coming from image transformation or neural networks, and the first results demonstrate that there is indeed a room for further improvement.

**Medium-term activities.** The results of the preceding paragraph are partial and have been obtained with a simple experimental approach only using off-the-shelf tools. We are thus encouraged to pursue research on combining expertise from dataflow programming languages and polyhedral compilation. Our long term objective is to go towards a formal framework to express, compile, and run dataflow applications with intrinsic instruction or pipeline parallelism.

We plan to investigate in the following directions:

- Investigate how polyhedral analysis extends on modular dataflow programs. For instance, how to modularize polyhedral scheduling analysis on our dataflow programs?

- Develop a proof of concept and validate it on linear algebra kernels (SVD, Gram-Schmidt, etc.).

- Explore various areas of applications from classical dataflow examples, like radio and video processing, to more recent applications in deep learning algorithmic. This will enable us to identify some potential (intra and extra) agent optimization patterns that could be leveraged into new language idioms.

**Long-term activities.** Current work focus on purely polyhedral applications. Irregular parts are not handled. Also, a notion of tiling is required so the communications of the dataflow program with the outside world can be tuned with respect to the local memory size. Hence, we plan to investigate the following points:

- Assess simple polyhedral/non polyhedral partitioning: How non-polyhedral parts can be hidden in processes/channels? How to abstract the dataflow dependencies between processes? What would be the impact on analyses? We target programs with irregular control (e.g., while loop, early exits) and regular data (arrays with affine accesses).

- Design tiling schemes for modular dataflow programs: What does it mean to tile a dataflow program? Which compiler algorithms to use?

- Implement a mature compiler infrastructure from the front-end to code generation for a reasonable subset of the representation.

#### 2.4 HLS-specific Dataflow Optimizations

- Objective: design a hardware optimizing compiler from our dataflow representation.

- Hard lock: **memory bandwith** ~>>> integrate additional HLS constraints such as communication costs.

The compiler analyses proposed in section 2.3 do not target a specific platform. In this part, we propose to leverage these analysis to develop source-level optimizations for high-level synthesis (HLS).

High-level synthesis consists in compiling a kernel written in a high-level language (typically in C) into a circuit. As for any compiler, an HLS tool consists in a *front-end* which translates the input kernel into an *intermediate representation*. This intermediate representation captures the control/flow dependences between computation units, generally in a hierarchical fashion. Then, the *back-end* maps this intermediate representation to a circuit (e.g. FPGA configuration). We believe that HLS tools must be thought as fine-grain automatic parallelizers. In classic HLS tools, the parallelism is expressed and exploited at the back-end level during the scheduling and the resource allocation of arithmetic operations. We believe that it would be far more profitable to derive the parallelism at the front-end level.

Hence, CASH will focus on the *front-end* pass and the *intermediate representation*. Low-level *back-end* techniques are not in the scope of CASH. Specifically, CASH will leverage the dataflow representation developed in Section 2.1 and the compilation techniques developed in Section 2.3 to develop a relevant intermediate representation for HLS and the corresponding front-end compilation algorithms.

Our results will be evaluated by using existing HLS tools (e.g., Intel HLS compiler, Xilinx Vivado HLS). We will implement our compiler as a source-to-source transformation in front of HLS tools. With this approach, HLS tools are considered as a "back-end black box". The CASH scheme is thus: (i) *frontend*: produce the CASH dataflow representation from the input C kernel. Then, (ii) turn this dataflow representation to a C program with pragmas for an HLS tool. This step must convey the characteristics of the dataflow representation found by step (i) (e.g. dataflow execution, fifo synchronisation, channel size). This source-to-source approach will allow us to get a full source-to-FPGA flow demonstrating the benefits of our tools while relying on existing tools for low-level optimizations. Step (i) will start from the DCC tool developed by Christophe Alias, which already produces a dataflow intermediate representation: the Data-aware Process Networks (DPN) [4]. Hence, the very first step is then to chose an HLS tool and to

investiguate which input should be fed to the HLS tool so it "respects" the parallelism and the resource allocation suggested by the DPN. From this basis, we plan to investiguate the points described thereafter.

*Roofline model and dataflow-level resource evaluation.* Operational intensity must be tuned according to the roofline model. The roofline model [57] must be redefined in light of FPGA constraints. Indeed, the peak performance is no longer constant: it depends on the operational intensity itself. The more operational intensity we need, the more local memory we use, the less parallelization we get (since FPGA resources are limited), and finally the less performance we get! Hence, multiple iterations may be needed before reaching an efficient implementation. To accelerate the design process, we propose to iterate at the dataflow program level, which implies a fast resource evaluation at the dataflow level.

*Reducing FPGA resources.* Each parallel unit must use as little resources as possible to maximize parallel duplication, hence the final performance. This requires to factorize the control and the channels. Both can be achieved with source-to-source optimizations at dataflow level. The main issue with outputs from polyhedral optimization is large piecewise affine functions that require a wide silicon surface on the FPGA to be computed. Actually we do not need to compute a closed form (expression that can be evaluated in bounded time on the FPGA) *statically.* We believe that the circuit can be compacted if we allow control parts to be evaluated dynamically. Finally, though dataflow architectures are a natural candidate, adjustments are required to fit FPGA constraints (2D circuit, few memory blocks). Ideas from systolic arrays [48] can be borrowed to re-use the same piece of data multiple times, despite the limitation to regular kernels and the lack of I/O flexibility. A trade-off must be found between pure dataflow and systolic communications.

*Improving circuit throughput.* Since we target streaming applications, the throughput must be optimized. To achieve such an optimization, we need to address the following questions. How to derive an optimal upper bound on the throughput for polyhedral process network? Which dataflow transformations should be performed to reach it? The limiting factors are well known: I/O (decoding of burst data), communications through addressable channels, and latencies of the arithmetic operators. Finally, it is also necessary to find the right methodology to measure the throughput statically and/or dynamically.

#### 2.4.1 Expected Impact

So far, the HLS front-end applies basic loop optimizations (unrolling, flattening, pipelining, etc.) and use a Hierarchical Control Flow Graph-like representation with data dependencies annotations (HCDFG). With this approach, we intend to demonstrate that polyhedral analysis combined with dataflow representations is an effective solution for HLS tools.

#### 2.4.2 Scientific Program

**Short-term and ongoing activities.** The HLS compiler designed in the CASH team currently extracts a fine-grain parallel intermediate representation (DPN [4, 3]) from a sequential program. We will not write a back-end that produces code for FPGA but we need to provide C programs that can be fed into existing C-to-FPGA compilers. However we obviously need an end-to-end compiler for our experiments. One of the first task of our HLS activity is to develop a DPN-to-C code generator suitable as input to an existing HLS tool like Vivado HLS. The generated code should exhibit the parallelism extracted by our compiler, and allow generating a final circuit more efficient than the one that would be generated by our target HLS tool if ran directly on the input program. Source-to-source approaches have already been experimented successfully, e.g. in Alexandru Plesco's PhD [44].

**Medium-term activities.** Our DPN-to-C code generation will need to be improved in many directions. The first point is the elimination of redundancies induced by the DPN model itself: buffers are duplicated to allow parallel reads, processes are produced from statements in the same loop, hence with the same control automaton. Also, multiplexing uses affine constraints which can be factorized [5]. We plan to study how these constructs can be factorized at C-level and to design the appropriate DPN-to-C translation algorithms.

Also, we plan to explore how on-the-fly evaluation can reduce the complexity of the control. A good starting point is the control required for the load process (which fetch data from the distant memory). If we want to avoid multiple load of the same data, the FSM (Finite State Machine) that describes it is usually very complex. We believe that dynamic construction of the load set (set of data to load from the main memory) will use less silicon than an FSM with large piecewise affine functions computed statically.

**Long-term activities.** The DPN-to-C compiler will open new research perspectives. We will explore the roofline model accuracy for different applications by playing on DPN parameters (tile size). Unlike the classical roofline model, the peak performance is no longer assumed to be constant, but decreasing with operational intensity [19]. Hence, we expect a *unique* optimal set of parameters. Thus, we will build a DPN-level cost model to derive an interval containing the optimal parameters.

Also, we want to develop DPN-level analysis and transformation to quantify the optimal reachable throughput and to reach it. We expect the parallelism to increase the throughput, but in turn it may require an operational intensity beyond the optimal point discussed in the first paragraph. We will assess the trade-offs, build the cost-models, and the relevant dataflow transformations.

#### 2.5 Simulation of Hardware

- Objective: design effective simulations for our low-level representations of programs, combined with precise models of hardware.

- Hard lock: **various simulation paradigms** → integrate heterogenous (and black-box) components in a unique setting.

Complex systems such as systems-on-a-chip or HPC computer with FPGA accelerator comprise both hardware and software parts, tightly coupled together. In particular, the software cannot be executed without the hardware, or at least a simulator of the hardware.

Because of the increasing complexity of both software and hardware, traditional simulation techniques (Register Transfer Level, RTL) are too slow to allow full system simulation in reasonable time. New techniques such as Transaction Level Modeling (TLM) [42] in SystemC [41] have been introduced and widely adopted in the industry. Internally, SystemC uses discrete-event simulation, with efficient context-switch using cooperative scheduling. TLM abstracts away communication details, and allows modules to communicate using function calls. We are particularly interested in the loosely timed coding style where the timing of the platform is not modeled precisely, and which allows the fastest simulations. This allowed gaining several orders of magnitude of simulation speed. However, SystemC/TLM is also reaching its limits in terms of performance, in particular due to its lack of parallelism.

Work on SystemC/TLM parallel execution is both an application of other work on parallelism in the team and a tool complementary to HLS presented in Sections 2.1 (dataflow models and programs) and 2.4 (application to FPGA). Indeed, some of the parallelization techniques we develop in CASH could apply to SystemC/TLM programs. Conversely, a complete design-flow based on HLS needs fast system-level simulation: the full-system usually contains both hardware parts designed using HLS, handwritten

hardware components, and software.

We will also work on simulation of the DPN intermediate representation. Simulation is a very important tool to help validate and debug a complete compiler chain. Without simulation, validating the front-end of the compiler requires running the full back-end and checking the generated circuit. Simulation can avoid the execution time of the backend and provide better debugging tools.

Automatic parallelization has shown to be hard, if at all possible, on loosely timed models [10]. We focus on semi-automatic approaches where the programmer only needs to make minor modifications of programs to get significant speedups.

#### 2.5.1 Expected Impact

The short term impact is the possibility to improve simulation speed with a reasonable additional programming effort. The amount of additional programming effort will thus be evaluated in the short term.

In the longer term, our work will allow scaling up simulations both in terms of models and execution platforms. Models are needed not only for individual Systems on a Chip, but also for sets of systems communicating together (e.g., the full model for a car which comprises several systems communicating together), and/or heterogeneous models. In terms of execution platform, we are studying both parallel and distributed simulations.

#### 2.5.2 Scientific Program

**Short-term and ongoing activities.** We started the joint PhD (with Tanguy Sassolas) of Gabriel Busnot with CEA-LIST. The research targets parallelizing SystemC heterogeneous simulations. CEA-LIST already developed SCale [55], which is very efficient to simulate parallel homogeneous platforms such as multicore chips. However, SCale cannot currently load-balance properly the computations when the platform contains different components modeled at various levels of abstraction. Also, SCale requires manual annotations to identify accesses to shared variables. These annotations are given as address ranges in the case of a shared memory. This annotation scheme does not work when the software does non-trivial memory management (virtual memory using a memory management unit, dynamic allocation), since the address ranges cannot be known statically. We started working on the "heterogeneous" aspect of simulations with an approach allowing changing the level of details in a simulation at runtime, and started tackling the virtual and dynamic memory management problem by porting Linux on our simulation platform.

We also started working on an improved support for simulation and debugging of the DPN internal representation of our parallelizing compiler (see Section 2.3). A previous quick experiment with simulation was to generate C code that simulates parallelism with POSIX-threads. While this simulator greatly helped debug the compiler, this is limited in several ways: simulations are not deterministic, and the simulator does not scale up since it would create a very large number of threads for a non-trivial design.

We are working in two directions. The first is to provide user-friendly tools to allow graphical inspection of traces. For example, we will work on the visualization of the sequence of steps leading to a deadlock when the situation occurs, and give hints on how to fix the problem in the compiler. The second is to use an efficient simulator to speed up the simulation. We plan to generate SystemC/TLM code from the DPN representation to benefit from the ability of SystemC to simulate a large number of processes.

**Medium-term activities.** Several research teams have proposed different approaches to deal with parallelism and heterogeneity. Each approach targets a specific abstraction level and coding style. While we do not hope for a universal solution, we believe that a better coordination of different actors of the domain could lead to a better integration of solutions. We could imagine, for example, a platform with one subsystem accelerated with SCale [55] from CEA-LIST, some compute-intensive parts delegated to sc-during [40] from Matthieu Moy, and a co-simulation with external physical solvers using SystemC-MDVP [8] from LIP6. We plan to work on the convergence of approaches, ideally both through point-to-point collaborations and with a collaborative project.

A common issue with heterogeneous simulation is the level of abstraction. Physical models only simulate one scenario and require concrete input values, while TLM models are usually abstract and not aware of precise physical values. One option we would like to investigate is a way to deal with loose information, e.g. manipulate intervals of possible values instead of individual, concrete values. This would allow a simulation to be symbolic with respect to the physical values.

Obviously, works on parallel execution of simulations would benefit to simulation of data-aware process networks (DPN). Since DPN are generated, we can even tweak the generator to guarantee some properties on the generated code, which will give us more freedom on the parallelization and partitioning techniques.

**Long-term activities.** In the long term, our vision is a simulation framework that will allow combining several simulators (not necessarily all SystemC-based), and allow running them in a parallel way. The Functional Mockup Interface (FMI) standard is a good basis to build upon, but the standard does not allow expressing timing and functional constraints needed for a full co-simulation to run properly.

# 3 Research group

Matthieu Moy is the current leader of the CASH "équipe centre". He is the proposed leader of the "equipe projet commune".

• Matthieu Moy. https://matthieu-moy.fr, assistant professor at Université Claude Bernard, Lyon 1 (UCBL). Matthieu received his PhD degree in Computer Science from Grenoble INP in 2005. During his PhD, he applied formal verification on models of Systems-on-a-Chip written in SystemC, as part of a collaboration with STMicroelectronics. After he joined Verimag/Ensimag as an assistant professor, he continued working with STMicroelectronics on various topics including formal verification, compilation techniques for SystemC, modeling of energy consumption and parallel execution of simulations. He presented part of his work on the subject to Collège de France with Laurent Maillet-Contoz from STMicroelectronics<sup>1</sup>.

He also worked on abstract interpretation and real-time calculus. Recently, his main research interest moved to critical systems on many-core architecture, including code generation from syn-chronous languages and timing analysis. He obtained his Habilitation (HDR) in 2014 from Grenoble INP, and became the leader of the "Synchrone" team in Verimag in 2015. He co-supervised 4 full PhDs (including 2 as main supervisor), and is now co-supervising 3 PhDs (2 as main supervisor).

• **Christophe Alias**. http://perso.ens-lyon.fr/christophe.alias, research associate (*Chargé de recherche*) at Inria. Christophe received his PhD degree in Computer Science from University of Versailles in 2005. His research focus on program analysis and compiler optimizations for high-performance computing, with a strong emphasis on polyhedral compilation techniques. He worked on many subjects around HPC compilers, including array SSA, vectorization, theory of loop tiling, data transfer optimization, buffer allocation, and dataflow models for high-level synthesis. He

<sup>&</sup>lt;sup>1</sup>http://www.college-de-france.fr/site/gerard-berry/seminar-2014-01-29-17h30.htm

co-supervised 2 PhD students: Alexandru Plesco on the compilation of data transfers for high-level synthesis, and Guillaume Iooss on semantic tiling. In 2011, he has co-founded with Cédric Bastoul the IMPACT international workshop which is now the annual reference event for the polyhedral compilation community. In 2014, he has co-founded with Alexandru Plesco the XtremLogic startup, which exploits the parallelizing compiler he wrote to synthesize circuits for FPGA.

- Laure Gonnord. http://laure.gonnord.org/pro/, assistant professor at Université Claude Bernard, Lyon 1 (UCBL). Laure received her PhD degree in computer science from the University Joseph Fourier (Grenoble), in 2007. She has been an assistant professor at the University of Lille, then at UCBL. Her main research interests lie in the design of static analyses, with emphasis on the automatic synthesis of numerical invariants and application in compilation (scheduling) and termination proofs. She has experience in the development of static analyses for synchronous programs. She coordinates the French Compilation Community (http://compilfr.ens-lyon.fr/). She obtained her Habilitation in 2017 from UCBL. She co-supervised 1 full PhD, and is from September 2018 co-supervising 2 PhD students.

- Ludovic Henrio. https://lhenrio.github.io/, research associate (CR1) at CNRS. Ludovic received his PhD degree from the University of Nice Sophia-Antipolis in 2003 and his habilitation thesis from the University of Nice Sophia-Antipolis in 2012. Ludovic Henrio was the scientific leader of the SCALE project at I3S (Sophia-Antipolis) and joined the LIP laboratory and the CASH team in October 2018. His research interests mostly focus on the formal study of programming languages for distributed systems, and on the application of formal methods to the verification of distributed applications and systems. In particular he worked on the theory of programming languages for distributed objects and components, but also on the application of formal methods to the static verification of distributed systems. He has experience in the semantics of programming languages and its use to assert the correctness of static analyses and runtime optimizations. He (co-)supervised 8 PhD students and is currently supervising 1 PhD student hosted at Huawei Technologies.

### **Participation Matrix**

The expected participation of members is depicted in Table 1. This participation matrix is indicative, we expect research directions to cross-fertilize and hence, the participation of members to vary in the future. Directions 2.1, 2.2 and 2.3 are the most transverse hence all members participate; directions 2.4 and 2.5 are more specific, which explains that not all members participate in it.

|                  | 2.1  | 2.2  | 2.3  | 2.4  | 2.5  |

|------------------|------|------|------|------|------|

| Christophe Alias | 10 % | 10 % | 30 % | 40 % | 10 % |

| Laure Gonnord    | 20 % | 60 % | 20 % |      |      |

| Ludovic Henrio   | 50 % | 30 % | 20 % |      |      |

| Matthieu Moy     | 20 % | 10 % | 10 % | 10 % | 50 % |

Table 1: Involvement of people of the team (Indicative percentages of the time of each participant)

## 4 Positioning with Respect to Other Research Teams

This section summarizes the main research teams working on the same topics as CASH. A more comprehensive list, with more details on the team's activities and how they relate to ours can be found in Appendix A. For the teams closest to CASH, the positioning text was discussed and validated by the corresponding team leader.

In the following, we use *Laboratory-Team* to refer to teams. For example, the team described in this document is LIP-CASH.

#### 4.1 Research themes and related teams within Inria

The current project proposal intends to make progress in the quest for performance of dataflow programs in particular on FPGAs, building upon the expertise of its members on algorithm design and formal methods.

The research teams that work in these domains in the Inria ecosystem are thus coming from two "themes" inside the "Algorithms, programs, software and architecture" field:

- Architecture, languages, compilation: especially CAMUS and CORSE, and to some extend PACAP.

- Embedded systems and real time: especially SPADES and PARKAS.

Some other Inria teams belonging to other themes have also some shared research themes: ANTIQUE, CELTIQUE, and SOCRATE.

#### 4.2 Large-scale Computing

Many teams target the optimized execution of applications on a large-scale infrastructure. Within the same laboratory as CASH (LIP), Avalon works on programming models and runtimes for distributed and HPC platforms. ROMA works on resource allocation and scheduling, and develops the massively parallel MUMPS software. DATAMOVE focuses on data-management in large-scale heterogeneous infrastructures.

These teams share the same final application domain as CASH, but deal with different issues. CASH focuses on small and medium-size computing kernels, and targets optimizations within one computing node. CASH follows a compilation and a language-based approach, and focuses on static optimizations, that are out of the scope of DATA, ROMA and DATAMOVE.

Outside France several teams work on language approaches for high-performance computing. For example the programming language research group in Uppsala works on actors with some datafloworiented synchronization patterns, and the Compiler Technology and Parallel Computing at PELAB in Linköping works on skeleton-based programming to optimize the execution of kernelson GPUs. CASH aims at a lower-level optimization, and target lower-level languages than these approaches, but we aim at collaborating with them.

#### 4.3 High Level Synthesis

We believe that High-Level Synthesis (HLS) is an understudied topic. It is studied in IRISA-CAIRN, TIMA-SLS, but both use an approach different from ours. One contribution of CASH is the cross-fertilization between the compilation and abstract interpretation communities. Also, CASH is more focused on static approaches and does not study the reconfigurability, while CAIRN targets dynamic reconfiguration management, and TIMA-SLS also focuses on task migration and context-switch.

Other teams and projects abroad include the VAST laboratory at University of California Los Angeles, the ROCCC project at University of California Riverside, the Circuits and Systems group at Imperial College or the Panda project at Politecnico di Milano. Most of these projects address all the aspects of circuit synthesis, from the design specification to low-level hardware generation. The goal of CASH is to follow a very focused research on HLS arround dataflow optimizations for HLS. A collaboration is possible with each of these teams.

### 4.4 Code Optimization and Execution

The added value of CASH in the compilation domain is the static-analysis based approach. Unlike LIG-CORSE and ICube-CAMUS, we do not consider dynamic approaches. We distinguish the analysis phase and the optimization phase and focus on the analysis more than the optimization.

### 4.5 Abstract Interpretation and Formal Methods

Abstract interpretation was initially studied for program verification, and applied to ensure the safety of programs, i.e. to prove properties of programs. DI-ENS-ANTIQUE, and its ancestors, is the team where abstract interpretation was invented, and applied successfully for example to prove the absence of numerical overflow in the primary flight control software of Airbus planes with the ASTREE tool. Verimag-PACSS has also expertise in abstract interpretation, with the same focus on program verification. We already collaborate with Verimag-PACSS, and started a joint PhD in Fall 2018.

What distinguishes CASH from these teams is the focus on low-cost analysis to allow more optimisation opportunities for compilers. We use abstract interpretation as a sound framework to perform compiler analysis and allow optimization passes to benefit from the invariants we compute. The "compilation" and "abstract interpretation" communities have traditionally been distant, and we want to benefit from the advances made in both.

To ensure sound bases for analysis, well-defined semantics are needed. Teams like LIP-PLUME have an expertise in the domain that will certainly benefit to CASH.

Other teams abroad include teams working on theoritical aspects of abstract interpretation, modelchecking and logics as well as their application to software verification: The Automatic Verification Research Group, at University of Oxford (UK), for instance, works on various topics linked with formal verification and correct-by-construction synthesis for software and hardware systems. The IMDEA Software lab, in Madrid (Spain) has expertise on the design of (expensive) logic-based program verification processes, but also on the development of models for cache and memory performance, which might inspire us.

#### 4.6 Dataflow

The dataflow formalism is studied in many contexts. It has successfully been applied in critical embedded systems through the Scade/Lustre language initially developed by the Verimag-Synchrone team. The synchronous dataflow paradigm was also used in similar contexts by DI-ENS-PARKAS and LIG-SPADES, who both used synchronous dataflow for embedded systems, and used it for parallel programming. The KIELER project in Kiel and the Informatics Theory Group in Bamberg also use synchronous languages for real-time embedded systems, but no not target high-performance computing. IRISA-TEA developed the Signal language on similar concepts.

CASH will build on the foundations built by these teams, but will apply the dataflow formalism outside the scope of embedded systems. The real-time guarantees provided by synchronous languages are not relevant in the context of CASH, but on the other hand the application of dataflow to HPC opens the door to many optimizations that are impossible on embedded systems.

CITI-SOCRATE also works on dataflow programming for compute-intensive applications. We collaborate on the subject with Lionel Morel. SOCRATE may also be a user of the tools CASH will produce.

Dataflow is also used in an HLS context by the Compaan project (spin-out from University Leiden), with an approach similar to the one of CASH. We target a more general representation than the Polyhedral Process Networks used in Compaan.

### 4.7 Simulation of Hardware

Fast simulation of hardware, in particular using SystemC, is a widely studied topic. LIP6-CIAN, CEA-LIST, and TIMA-SLS, are the main French actors in the domain. They all work on techniques to improve simulation speed: parallelism for LIP6-CIAN and CEA-LIST, native simulation of software for TIMA-SLS. The activities of TIMA-SLS are disjoint to ours, but the "simulation" research direction of CASH has a lot in common with LIP6-CIAN and CEA-LIST. Indeed, we already co-supervise a PhD with LIST, and plan to collaborate with CIAN.

Non-french actors include the team of Rolf Drechsler (Bremen), Reiner Leupers (Aachen) and Rainer Dömer (California). Most work by these teams target models written at a lower level than the ones we consider in CASH.

# 5 Industrial collaborations

The CASH team follows a case-study driven approach. In some cases, well-established benchmarks exist and summarize typical programs encountered in real-life applications. Examples include Polybench/C [45] for the polyhedral model or the LLVM test suite for general programs. Another way to direct our research towards the needs of end-users is industrial collaborations. The primary goal of industrial collaborations for CASH is to keep our research in sync with the current needs and practices of the industry. We hope to collaborate with industrials with both collaborative projects and point-to-point contracts like CIFRE PhDs. One key to the success of this strategy is to recruit good master students, since negotiating a CIFRE PhD showed to be much easier once a good student is identified.

We detail below the relationships we currently have with industrial partners, but we hope to establish new partnerships with other companies in the future.

### 5.1 XtremLogic

Christophe Alias has a strong relationship with XtremLogic, a startup that he cofounded with one of his former PhD student, Alexandru Plesco. XtremLogic develops a complete hardware compiler from C to Verilog, which was initially developed in the context of the PhD of Alexandru Plesco. Christophe is the sole author of the polyhedral compiler that was partially transferred to XtremLogic in April 2014 under an "Inria exclusive License". Since this date, Christophe is linked to XtremLogic by a "convention de concours scientifique Inria", and spends 20% of his time at XtremLogic as "conseiller scientifique" (scientific consultant).

The CASH team as a whole will strongly benefit from this proximity, but the collaboration will be done respecting our "research" identity and taking into account potential conflicts of interests. We make a clear distinction between the work done by XtremLogic in an industrial context and the research done in CASH.

The proximity with XtremLogic gives the CASH team indirect access to end-users, and allows the team to get a better understanding of the current needs and practical challenges in the area of High-Level Synthesis for High-Performance Computing. This will greatly help the CASH team in its "case-study driven" approach (we do not have access to actual case-studies, which are confidential). From a scientific point of view, even though XtremLogic is a commercial entity, there are still major scientific challenges to solve.

### 5.2 STMicroelectronics

Matthieu Moy has a long term collaboration with STMicroelectronics since 2002 on simulation of systemson-chips. Topics studied as part of this collaboration include formal verification of SystemC programs, modeling techniques to ensure faithfulness with respect to functional properties, and extra-functional properties like time, power-consumption and temperature, and parallelism.

We are still in contact with the team at STMicroelectronics (in particular Laurent Maillet-Contoz and Jérôme Cornet), and plan to continue this collaboration. Hot current topics include parallel and distributed simulation, and relationship between modeling and high-level synthesis (since the same language can be used in the model and the implementation, models are much easier to write).

## 5.3 Kalray

Laure Gonnord started a collaboration on the SigmaC compiler in 2016, with Lionel Morel (CEA Grenoble). Matthieu Moy has an experience on the MPPA architecture and he collaborates with Kalray on hard-real time topics. The research directions on this topic are detailed in Section 2.3. We started discussions on possible future collaborations on the compilation and analysis of OpenMP programs to optimize the execution of loops for the MPPA architecture.

# 6 Relevant publications of the team members

Some relevant publications of the future team members.

- Polyhedral Dataflow Programming: a Case Study. Romain Fontaine, Laure Gonnord and Lionel Morel, SBAC-PAD 2018.

- Improving Comunication Patterns in Polyhedral Process Networks. Christophe Alias, HiP3ES 2018.

- Optimizing Affine Control with Semantic Factorizations. **Christophe Alias** and Alexandru Plesco, ACM Transactions on Architecture and Code Optimization (TACO), 2017.